|

| fsp_err_t | R_LAYER3_SWITCH_Open (ether_switch_ctrl_t *const p_ctrl, ether_switch_cfg_t const *const p_cfg) |

| |

| fsp_err_t | R_LAYER3_SWITCH_Close (ether_switch_ctrl_t *const p_ctrl) |

| | Disables interrupts and stop module. Implements ether_switch_api_t::close. More...

|

| |

| fsp_err_t | R_LAYER3_SWITCH_CreateDescriptorQueue (ether_switch_ctrl_t *const p_ctrl, uint32_t *const p_queue_index, const layer3_switch_descriptor_queue_cfg_t *const p_queue_cfg) |

| | Create a new descriptor queue and set it to LINKFIX table. This function must be called before calling R_LAYER3_SWITCH_SetDescriptor and R_LAYER3_SWITCH_GetDescriptor. More...

|

| |

| fsp_err_t | R_LAYER3_SWITCH_SetDescriptor (ether_switch_ctrl_t *const p_ctrl, uint32_t queue_index, layer3_switch_descriptor_t const *const p_descriptor) |

| | Set descriptor data to a target descriptor. More...

|

| |

| fsp_err_t | R_LAYER3_SWITCH_GetDescriptor (ether_switch_ctrl_t *const p_ctrl, uint32_t queue_index, layer3_switch_descriptor_t *const p_descriptor) |

| | Get descriptor data from a target descriptor. More...

|

| |

| fsp_err_t | R_LAYER3_SWITCH_StartDescriptorQueue (ether_switch_ctrl_t *const p_ctrl, uint32_t queue_index) |

| | Reload and enable a descriptor queue. In a TX descriptor queue, the queue start transmission. In a RX descriptor queue, the queue start reception. More...

|

| |

| fsp_err_t | R_LAYER3_SWITCH_CallbackSet (ether_switch_ctrl_t *const p_ctrl, void(*p_callback)(ether_switch_callback_args_t *), void *const p_context, ether_switch_callback_args_t *const p_callback_memory) |

| |

| fsp_err_t | R_LAYER3_SWITCH_ConfigurePort (ether_switch_ctrl_t *const p_ctrl, uint8_t port, layer3_switch_port_cfg_t *p_port_cfg) |

| |

| fsp_err_t | R_LAYER3_SWITCH_AddTableEntry (ether_switch_ctrl_t *const p_ctrl, layer3_switch_frame_filter_t const *const p_target_frame, layer3_switch_table_entry_cfg_t const *const p_entry_cfg) |

| |

| fsp_err_t | R_LAYER3_SWITCH_SearchTableEntry (ether_switch_ctrl_t *const p_ctrl, layer3_switch_frame_filter_t const *const p_target_frame, layer3_switch_table_entry_cfg_t *const p_entry_cfg) |

| |

| fsp_err_t | R_LAYER3_SWITCH_ConfigureTable (ether_switch_ctrl_t *const p_ctrl, layer3_switch_table_cfg_t const *const p_table_cfg) |

| |

| fsp_err_t | R_LAYER3_SWITCH_GetTable (ether_switch_ctrl_t *const p_ctrl, layer3_switch_table_t *const p_table) |

| |

| fsp_err_t | R_LAYER3_SWITCH_ConfigureTAS (ether_switch_ctrl_t *const p_ctrl, uint8_t port, layer3_switch_tas_cfg_t *p_tas_cfg) |

| |

| fsp_err_t | R_LAYER3_SWITCH_EnableTAS (ether_switch_ctrl_t *const p_ctrl, uint8_t port) |

| |

| fsp_err_t | R_LAYER3_SWITCH_PsfpClearErrorStatus (ether_switch_ctrl_t *const p_ctrl, layer3_switch_psfp_error_status_bitmask_t bitmasks) |

| |

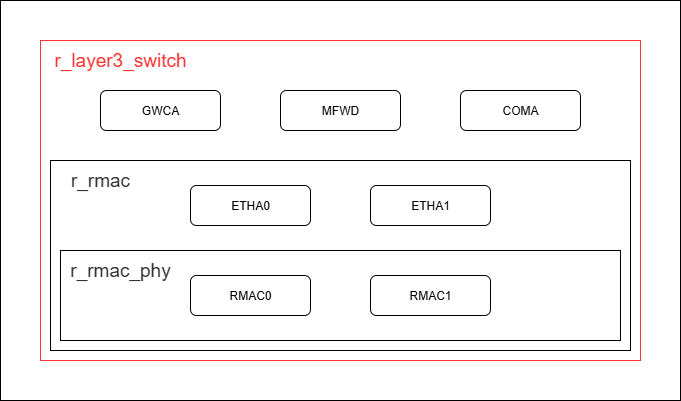

The LAYER3 SWITCH module (r_layer3_switch) provides an API for standard Ethernet communications applications that use the ESWM peripheral. It implements the Ethernet Switch Interface.

Overview

This module performs Ethernet frame transmission and reception using Ethernet Switch Module.

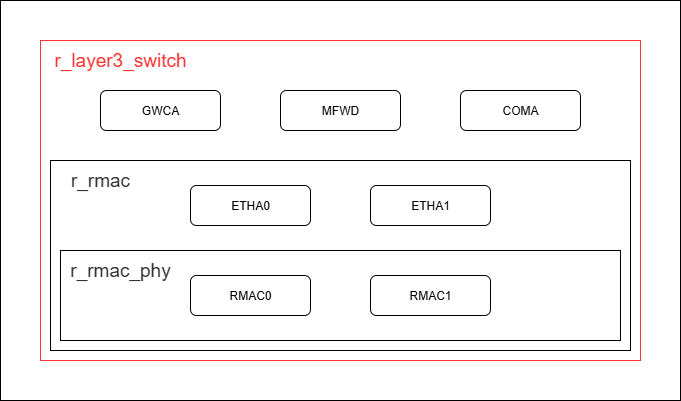

The following figure shows which IPs are used by the r_layer3_switch module.

ESWM block diagram

Features

The layer3 switch module supports the following features:

- Transmit/receive data using a descriptor.

- Timestamp feature

- Optional callback function when transmit/receive complete or an error occurs

- Port based Forwarding [MFWD]

- Direct Forwarding [MFWD]

- L2/L3 Forwarding [MFWD/GWCA]

- L2/L3 Update [MFWD]

- Frame Replication and Elimination for Reliability (FRER) feature [MFWD]

- Per Stream Filtering and Policing (PSFP) feature [MFWD]

Supported Devices

| Device Group | Devices |

| RA8 | RA8D2, RA8M2, RA8P1, RA8T2 |

Configuration

Build Time Configurations for r_layer3_switch

The following build time configurations are defined in fsp_cfg/r_layer3_switch_cfg.h:

| Configuration | Options | Default | Description |

| Parameter Checking |

-

Default (BSP)

-

Enabled

-

Disabled

| Default (BSP) | If selected code for parameter checking is included in the build. |

| Available queue num | Value must be an integer between 1 and 64 | 4 | available queue num. |

| gPTP enable |

| Enabled | Select whether or not to use gPTP function. |

| Time Aware Shaper |

| Disabled | Select whether or not to use the Time Aware Shaper function. |

Configurations for Networking > Switch (r_layer3_switch)

This module can be added to the Stacks tab via New Stack > Networking > Switch (r_layer3_switch). Non-secure callable guard functions can be generated for this module by right clicking the module in the RA Configuration tool and checking the "Non-secure Callable" box.

| Configuration | Options | Default | Description |

| Interrupts |

| Interrupt priority | MCU Specific Options | | Select the layer3_switch interrupt priority. |

| ETHA0 error interrupt priority | MCU Specific Options | | Select the layer3_switch etha0 interrupt priority. |

| ETHA1 error interrupt priority | MCU Specific Options | | Select the layer3_switch etha1 interrupt priority. |

| Ports |

| Ports > Port 0 |

| Ports > Port 0 > IPV queue depth |

| Queue 0 | Value must be an integer more than 1 | 64 | queue0 dept of port 0. |

| Queue 1 | Value must be an integer more than 1 | 64 | queue1 dept of port 0. |

| Queue 2 | Value must be an integer more than 1 | 64 | queue2 dept of port 0. |

| Queue 3 | Value must be an integer more than 1 | 64 | queue3 dept of port 0. |

| Queue 4 | Value must be an integer more than 1 | 64 | queue4 dept of port 0. |

| Queue 5 | Value must be an integer more than 1 | 64 | queue5 dept of port 0. |

| Queue 6 | Value must be an integer more than 1 | 64 | queue6 dept of port 0. |

| Queue 7 | Value must be an integer more than 1 | 64 | queue7 dept of port 0. |

| Forwarding | MCU Specific Options | | Destination ports for port 0 forwarding |

| IPV queues for preemptable frames |

-

Queue 0

-

Queue 1

-

Queue 2

-

Queue 3

-

Queue 4

-

Queue 5

-

Queue 6

-

Queue 7

| | Select IPV queues that send preemptable frames from port 0. |

| Minimum fragment size of preemptable frames |

-

64 bytes

-

128 bytes

-

192 bytes

-

256 bytes

| 64 bytes | Select minimum fragment size of preemptable frames that send from port 0. |

| MAC address | Must be a valid MAC address | 00:11:22:33:44:55 | MAC address of port 0. |

| Callback | Name must be a valid C symbol | NULL | Callback provided when an ISR occurs for port0. |

| Context | Name must be a valid C symbol | NULL | Placeholder for user data. Passed to the user callback in ether_switch_callback_args_t for port0. |

| GPTP timer number |

| Timer 0 | GPTP timer number of port 0. |

| Ports > Port 1 |

| Ports > Port 1 > IPV queue depth |

| Queue 0 | Value must be an integer more than 1 | 64 | queue0 dept of port 1. |

| Queue 1 | Value must be an integer more than 1 | 64 | queue1 dept of port 1. |

| Queue 2 | Value must be an integer more than 1 | 64 | queue2 dept of port 1. |

| Queue 3 | Value must be an integer more than 1 | 64 | queue3 dept of port 1. |

| Queue 4 | Value must be an integer more than 1 | 64 | queue4 dept of port 1. |

| Queue 5 | Value must be an integer more than 1 | 64 | queue5 dept of port 1. |

| Queue 6 | Value must be an integer more than 1 | 64 | queue6 dept of port 1. |

| Queue 7 | Value must be an integer more than 1 | 64 | queue7 dept of port 1. |

| Forwarding | MCU Specific Options | | Destination ports for port 1 forwarding |

| IPV queues for preemptable frames |

-

Queue 0

-

Queue 1

-

Queue 2

-

Queue 3

-

Queue 4

-

Queue 5

-

Queue 6

-

Queue 7

| | Select IPV queues that send preemptable frames from port 1. |

| Minimum fragment size of preemptable frames |

-

64 bytes

-

128 bytes

-

192 bytes

-

256 bytes

| 64 bytes | Select minimum fragment size of preemptable frames that send from port 1. |

| MAC address | Must be a valid MAC address | 00:11:22:33:44:55 | MAC address of port 1. |

| Callback | Name must be a valid C symbol | NULL | Callback provided when an ISR occurs for port1. |

| Context | Name must be a valid C symbol | NULL | Placeholder for user data. Passed to the user callback in ether_switch_callback_args_t for port1. |

| GPTP timer number |

| Timer 1 | GPTP timer number of port 1. |

| Ports > CPU |

| Forwarding |

| | Destination ports for CPU forwarding |

| CBS |

| CBS > Port 0 Band width ( % ) |

| Queue 0 | Value must be an integer between 0 and 100 | 0 | queue0 Band width of port 0. |

| Queue 1 | Value must be an integer between 0 and 100 | 0 | queue1 Band width of port 0. |

| Queue 2 | Value must be an integer between 0 and 100 | 0 | queue2 Band width of port 0. |

| Queue 3 | Value must be an integer between 0 and 100 | 0 | queue3 Band width of port 0. |

| Queue 4 | Value must be an integer between 0 and 100 | 0 | queue4 Band width of port 0. |

| Queue 5 | Value must be an integer between 0 and 100 | 0 | queue5 Band width of port 0. |

| Queue 6 | Value must be an integer between 0 and 100 | 0 | queue6 Band width of port 0. |

| Queue 7 | Value must be an integer between 0 and 100 | 0 | queue7 Band width of port 0. |

| CBS > Port 1 Band width ( % ) |

| Queue 0 | Value must be an integer between 0 and 100 | 0 | queue0 Band width of port 1. |

| Queue 1 | Value must be an integer between 0 and 100 | 0 | queue1 Band width of port 1. |

| Queue 2 | Value must be an integer between 0 and 100 | 0 | queue2 Band width of port 1. |

| Queue 3 | Value must be an integer between 0 and 100 | 0 | queue3 Band width of port 1. |

| Queue 4 | Value must be an integer between 0 and 100 | 0 | queue4 Band width of port 1. |

| Queue 5 | Value must be an integer between 0 and 100 | 0 | queue5 Band width of port 1. |

| Queue 6 | Value must be an integer between 0 and 100 | 0 | queue6 Band width of port 1. |

| Queue 7 | Value must be an integer between 0 and 100 | 0 | queue7 Band width of port 1. |

| CBS > Port 0 Maximum burst frame number |

| Queue 0 | Value must be an integer between 0 and 255 | 0 | queue0 maximum burst frame number of port 0. |

| Queue 1 | Value must be an integer between 0 and 255 | 0 | queue1 maximum burst frame number of port 0. |

| Queue 2 | Value must be an integer between 0 and 255 | 0 | queue2 maximum burst frame number of port 0. |

| Queue 3 | Value must be an integer between 0 and 255 | 0 | queue3 maximum burst frame number of port 0. |

| Queue 4 | Value must be an integer between 0 and 255 | 0 | queue4 maximum burst frame number of port 0. |

| Queue 5 | Value must be an integer between 0 and 255 | 0 | queue5 maximum burst frame number of port 0. |

| Queue 6 | Value must be an integer between 0 and 255 | 0 | queue6 maximum burst frame number of port 0. |

| Queue 7 | Value must be an integer between 0 and 255 | 0 | queue7 maximum burst frame number of port 0. |

| CBS > Port 1 Maximum burst frame number |

| Queue 0 | Value must be an integer between 0 and 255 | 0 | queue0 maximum burst frame number of port 0. |

| Queue 1 | Value must be an integer between 0 and 255 | 0 | queue1 maximum burst frame number of port 0. |

| Queue 2 | Value must be an integer between 0 and 255 | 0 | queue2 maximum burst frame number of port 0. |

| Queue 3 | Value must be an integer between 0 and 255 | 0 | queue3 maximum burst frame number of port 0. |

| Queue 4 | Value must be an integer between 0 and 255 | 0 | queue4 maximum burst frame number of port 0. |

| Queue 5 | Value must be an integer between 0 and 255 | 0 | queue5 maximum burst frame number of port 0. |

| Queue 6 | Value must be an integer between 0 and 255 | 0 | queue6 maximum burst frame number of port 0. |

| Queue 7 | Value must be an integer between 0 and 255 | 0 | queue7 maximum burst frame number of port 0. |

| Name | Name must be a valid C symbol | g_layer3_switch0 | Module name. |

| Channel | 0 | 0 | Select the layer3 switch controller channel number. |

| Context | Name must be a valid C symbol | NULL | Placeholder for user data. Passed to the user callback in ether_switch_callback_args_t. |

| Callback | Name must be a valid C symbol | NULL | Callback provided when an ISR occurs |

| Number of Layer 3 routing entries | Value must be an integer between 1 and 256 | 10 | Maximum number of Layer 3 routing entries. |

Usage Notes

Time-Sensitive Network (TSN)

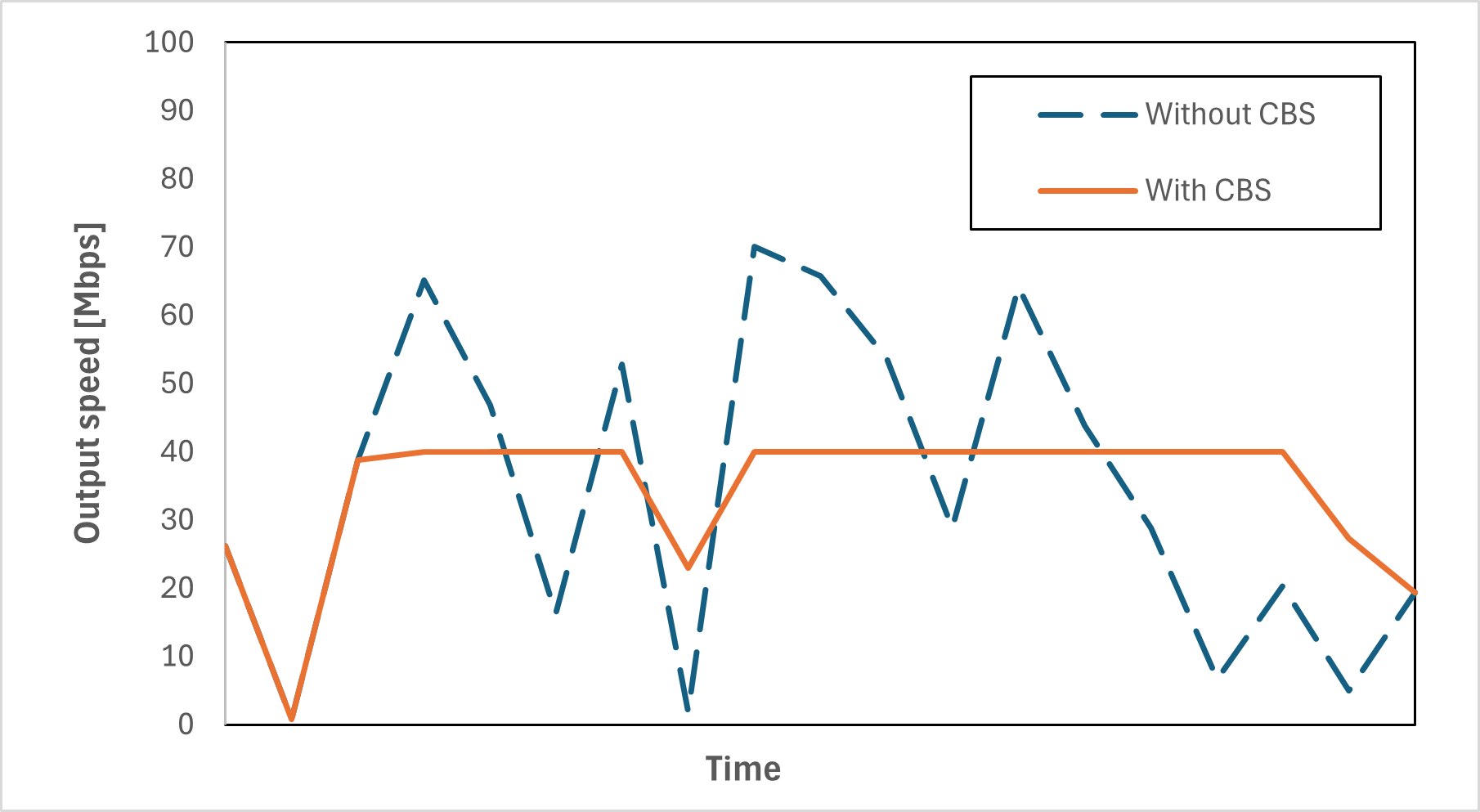

Credit Based Shaper [802.1Qav]

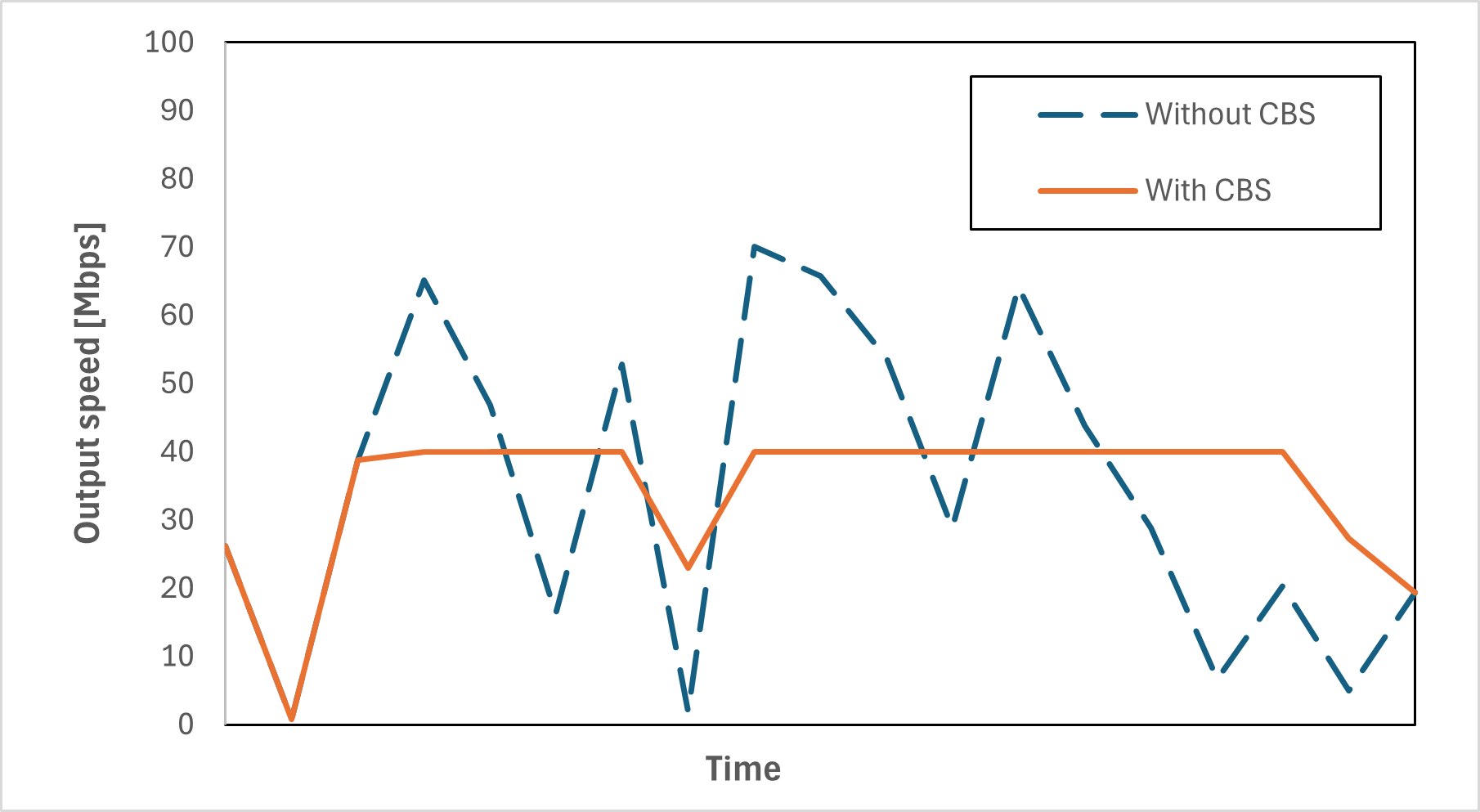

Credit Based Shaper (CBS) is a standard defined in IEEE 802.1Qav that limits the throughput of Ethernet traffic. The figure below illustrates the operation of CBS when the bandwidth is set to 40Mbps. When the transmission throughput exceeds the bandwidth configured by CBS, frame transmission is restricted. The restricted frames are buffered in the queue and transmitted with delay.

CBS operation image

In the r_layer3_switch module, CBS bandwidth can be configured for each Internal Priority Value (IPV) queue per transmission port. There are 8 IPV queues available for each port. On transmission ports where CBS is enabled, the throughput is limited to the configured bandwidth. CBS can be configured through stack properties or the ConfigurePort() API.

- Note

- The maximum number of frames that can be buffered by CBS is limited to the depth of each IPV queue. If many frames are buffered in high-priority queues, the common memory pool may be depleted, potentially limiting transmission from other queues.

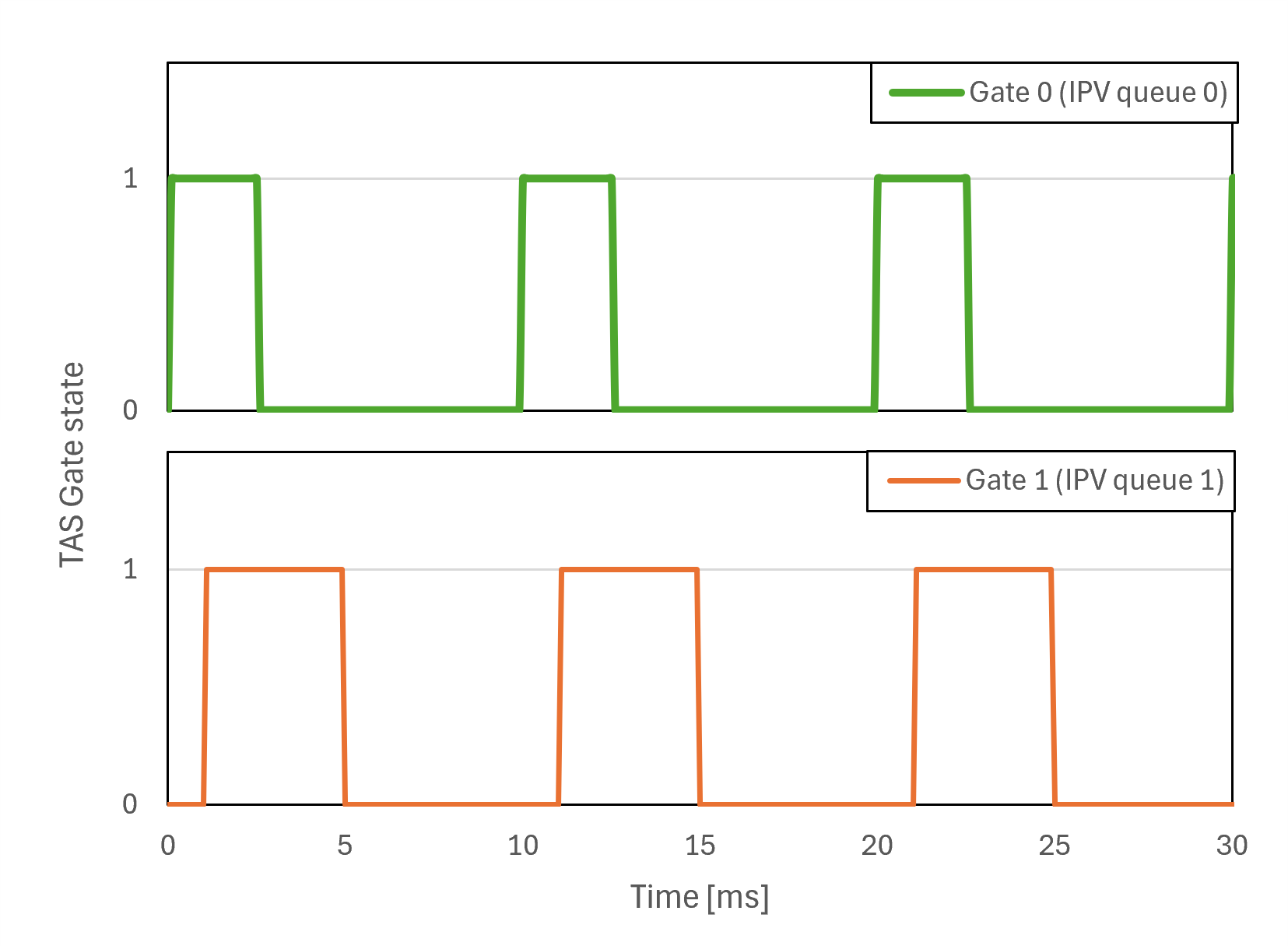

Time-Aware Shaper [802.1Qbv]

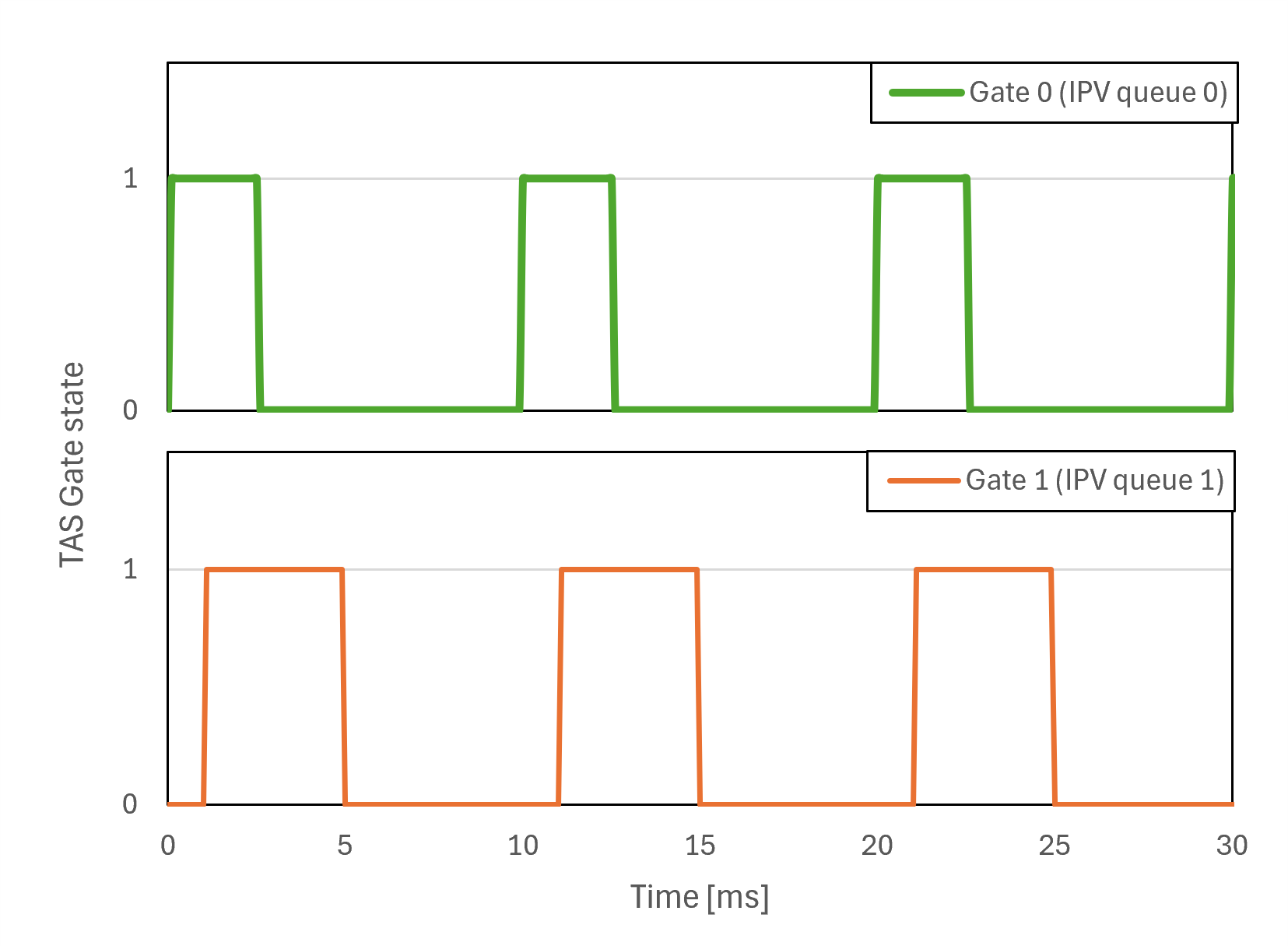

Time-Aware Shaper (TAS) is a standard defined in IEEE 802.1Qbv that limits Ethernet traffic by controlling the time window when frames are transmitted. TAS controls transmission by changing gate states. Frames are transmitted while the gate is opened and when the gate is closed, frames cannot be transmitted and are delayed until the next open state. By opening each gate at different timings, it is possible to prevent frames of specific priorities from monopolizing the bandwidth. The figure below illustrates the operation of TAS. In this image, the gate cycle time is set to 10ms, Gate 0 is opened for 2.5 ms and closed for 7.5 ms, Gate 1 is closed for 1.0 + 5.0 ms and open for 4.0 ms.

TAS operation image

In the r_layer3_switch module, TAS gates can be configured for each IPV queue of the transmission ports. Each gate learns entries that represent windows. An entry contains the window time and state. TAS feature is configured using the ConfigureTAS() API, and enabled using the EnableTAS() API.

- Note

- This TAS feature uses the gPTP timer.

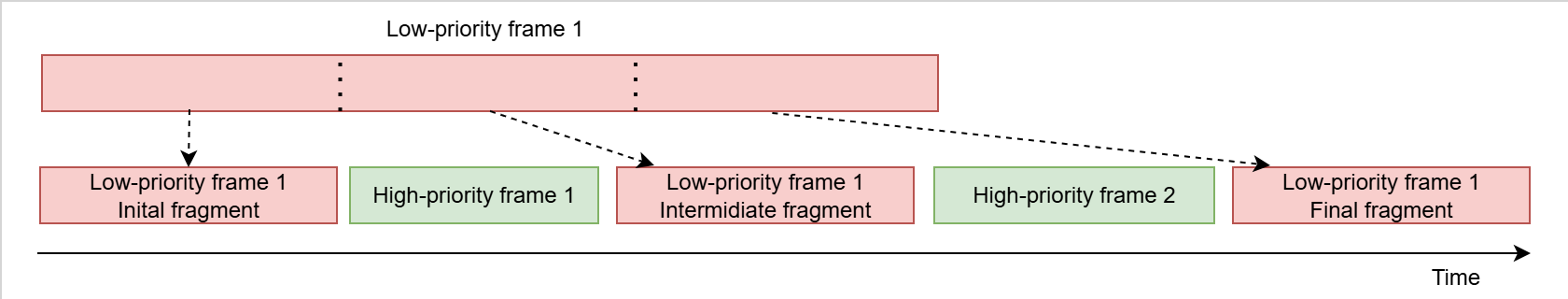

Frame preemption [802.3br, 802.1Qbu]

Frame preemption is a standard defined in IEEE 802.3br and 802.1Qbu. This standard allows preempting low-priority frames to send high-priority frames.

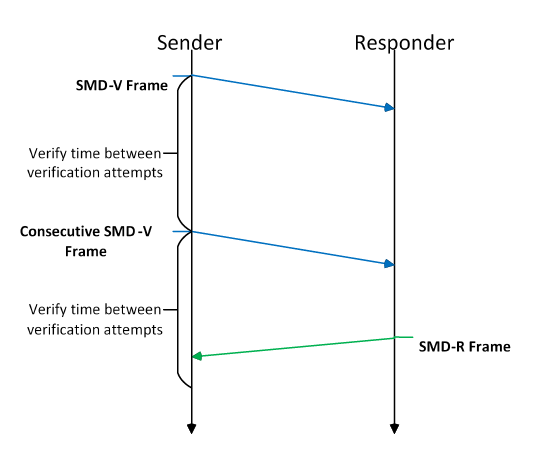

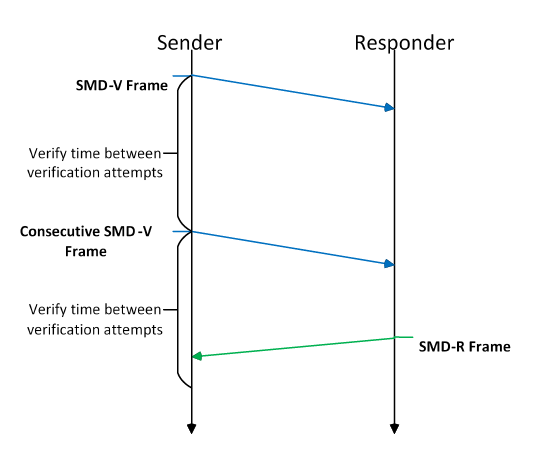

Verification process

Frame preemption needs to verify the frame preemption capability of the link partner. The figure below shows the verification process. Verify frames have special preambles, so these frames are rejected on devices which do not support frame preemption.

Frame preemption verification

In the r_layer3_switch module, the verification process is performed when the r_rmac_phy module links up and frame preemption is enabled in the configuration.

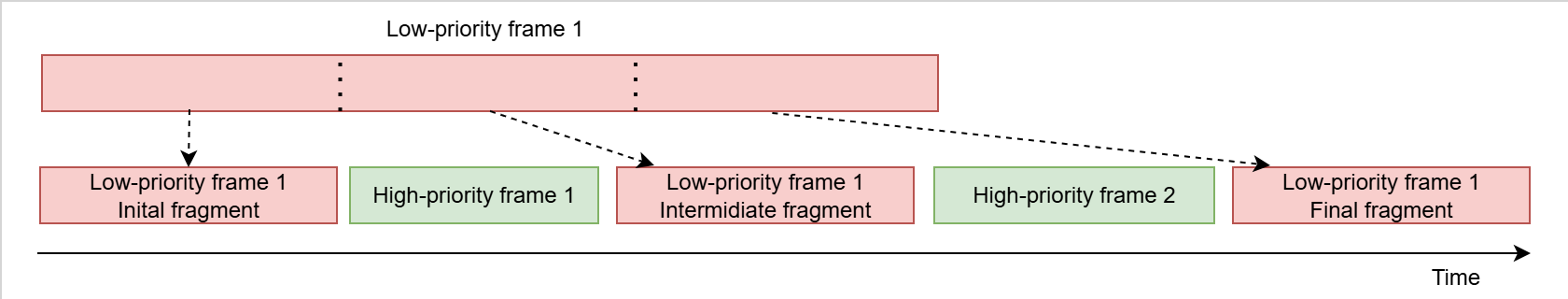

Preemption

The figure below shows the behavior of frame preemption. The low-priority frame (preemptable frame) is separated into several fragments, and they can be transferred in the intervals between high-priority frames (express frames). As a result, the negative influence on the throughput of high-priority frames is prevented.

Frame preemption behavior

In the r_layer3_switch module, each IPV queue can be configured to send either preemptable frames or express frames. ESWM IP automatically assembles separated frames when receiving them.

- Note

- Sending preemptable frames is enabled when the verification process succeeds.

Per Stream Filtering and Policing (PSFP) [802.1Qci]

Per Stream Filtering and Policing (PSFP) feature is a standard defined in IEEE 802.1Qci that supports MSDU and Meter filters.

MAC Service Data Unit (MSDU) Filter

MAC Service Data Unit (MSDU)filter filters packets when Ethernet frame size (payload) is more than a threshold.

Meter Filter

Meter filter filters packets when information rate is more than a threshold.

The filtered packets are sent to green or yellow bucket by Meter filter configuration.

Normal Mode and Throttle Mode

MSDU and Meter filters support normal mode and throttle mode.

In normal mode, the driver does not send packets filtered MSDU or Meter filter. Also, error status flag becomes 1 when the packet is more than a threshold.

In throttle mode, the driver keeps not to send all packets when error status flag is 1. User can clear error status flag using PsfpClearErrorStatus() API.

Limitations

Developers should be aware of the following limitations when using the r_layer3_switch:

- CBS feature supports only 100 Mbps and 1 Gbps link speeds.

- PSFP feature supports only Meter filter and MSDU filter. PSFP stream gates are not supported.

Examples

Basic Example

This is a basic example of transmission use of the LAYER3 SWITCH.

#define LAYER3_SWITCH_EXAMPLE_DESCRIPTOR_POOL_SIZE (8)

#define LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE (1514)

#define LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_UPPER ((uint8_t) ((LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE & \

0xFF00) >> 8))

#define LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_LOWER ((uint8_t) LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE & \

0x00FF)

#define LAYER3_SWITCH_EXAMPLE_TRANSMIT_ETHERNET_FRAME_SIZE (60)

#define LAYER3_SWITCH_EXAMPLE_SOURCE_MAC_ADDRESS 0x74, 0x90, 0x50, 0x00, 0x79, 0x01

#define LAYER3_SWITCH_EXAMPLE_DESTINATION_MAC_ADDRESS 0x74, 0x90, 0x50, 0x00, 0x79, 0x02

#define LAYER3_SWITCH_EXAMPLE_FRAME_TYPE 0x00, 0x2E

#define LAYER3_SWITCH_EXAMPLE_PAYLOAD 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, \

0x00, \

0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, \

0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, \

0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00

uint8_t gp_ether_buffer0[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t gp_ether_buffer1[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t gp_ether_buffer2[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t gp_ether_buffer3[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t gp_ether_buffer4[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t gp_ether_buffer5[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t gp_ether_buffer6[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t gp_ether_buffer7[LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE];

uint8_t * gpp_ether_buffers[8] =

{

&gp_ether_buffer0[0],

&gp_ether_buffer1[0],

&gp_ether_buffer2[0],

&gp_ether_buffer3[0],

&gp_ether_buffer4[0],

&gp_ether_buffer5[0],

&gp_ether_buffer6[0],

&gp_ether_buffer7[0],

};

uint8_t gp_send_data[LAYER3_SWITCH_EXAMPLE_TRANSMIT_ETHERNET_FRAME_SIZE] =

{

LAYER3_SWITCH_EXAMPLE_DESTINATION_MAC_ADDRESS,

LAYER3_SWITCH_EXAMPLE_SOURCE_MAC_ADDRESS,

LAYER3_SWITCH_EXAMPLE_FRAME_TYPE,

LAYER3_SWITCH_EXAMPLE_PAYLOAD

};

void layer3_switch_transmit_example (void)

{

uint32_t queue_index = 0;

{

.p_descriptor_array = gp_descriptor_pool,

.p_ts_descriptor_array = NULL,

.array_length = LAYER3_SWITCH_EXAMPLE_DESCRIPTOR_POOL_SIZE,

};

memcpy(gpp_ether_buffers[0], gp_send_data, LAYER3_SWITCH_EXAMPLE_TRANSMIT_ETHERNET_FRAME_SIZE);

transmission_descriptor.basic.ds_l = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_LOWER;

transmission_descriptor.basic.ds_h = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_UPPER;

transmission_descriptor.basic.die = 1;

transmission_descriptor.basic.ptr_l = (uintptr_t) gpp_ether_buffers;

transmission_descriptor.info1_tx.fmt = 1;

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

do

{

} while (FSP_SUCCESS != err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

}

This is a basic example of reception use of the LAYER3 SWITCH.

#define LAYER3_SWITCH_EXAMPLE_RECEPTION_QUEUE_LENGTH (4)

bool g_complete_reception_flag;

void layer3_switch_receive_example (void)

{

uint32_t queue_index = 1;

{

.p_descriptor_array = gp_descriptor_pool,

.p_ts_descriptor_array = NULL,

.array_length = LAYER3_SWITCH_EXAMPLE_DESCRIPTOR_POOL_SIZE,

};

reception_descriptor.basic.ds_l = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_LOWER;

reception_descriptor.basic.ds_h = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_UPPER;

reception_descriptor.basic.die = 1;

reception_descriptor.basic.ptr_l = (uintptr_t) gpp_ether_buffers;

reception_descriptor.info1_tx.fmt = 1;

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

do

{

} while (FSP_SUCCESS != err);

assert(FSP_SUCCESS == err);

for (uint16_t i = 0; i < LAYER3_SWITCH_EXAMPLE_RECEPTION_QUEUE_LENGTH - 1; i++)

{

memset(gpp_ether_buffers[i], 0, LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE);

reception_descriptor.basic.ptr_l = (uintptr_t) gpp_ether_buffers[i];

assert(FSP_SUCCESS == err);

}

g_complete_reception_flag = false;

assert(FSP_SUCCESS == err);

while (true != g_complete_reception_flag)

{

}

assert(FSP_SUCCESS == err);

}

{

{

g_complete_reception_flag = true;

break;

}

{

break;

}

{

break;

}

{

break;

}

default:

{

break;

}

}

}

TSN Example

The below is an example of forwarding frames with Credit Based Shaper (CBS).

void layer3_switch_cbs_example (void)

{

uint8_t source_port = 0;

uint8_t destination_port = 1;

{

.max_burst_num_list = {10, 10, 10, 10, 10, 10, 10, 10 },

};

uint8_t p_mac_address_list[2][6] =

{

{0x00, 0x01, 0x02, 0x03, 0x04, 0x05, },

{0x10, 0x11, 0x12, 0x13, 0x14, 0x15, },

};

{

.unsecure_entry_maximum_num = 2,

};

{

.source_ports = (1 << source_port),

.internal_priority_update_enable = true,

.entry_enable = true,

};

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

for (uint8_t i = 0; i < 2; i++)

{

assert(FSP_SUCCESS == err);

}

assert(FSP_SUCCESS == err);

while (1)

{

}

}

The below is an example of forwarding frames with Time Aware Shaper (TAS).

#define LAYER3_SWITCH_EXAMPLE_GPTP_TIMER (0)

#define LAYER3_SWITCH_EXAMPLE_GPTP_CLOCK_PERIOD (4)

void layer3_switch_tas_example (void)

{

uint8_t source_port = 0;

uint8_t destination_port = 1;

{

.p_tas_entry_list = closed_entry_list

};

gptp_instance_t const * p_gptp_instance = g_layer3_switch0_extended_cfg.p_gptp_instance;

assert(FSP_SUCCESS == err);

tas_cfg.

gate_cfg_list[0] = g_layer3_switch_example_tas_gate_0_cfg;

tas_cfg.

gate_cfg_list[1] = g_layer3_switch_example_tas_gate_1_cfg;

for (uint8_t i = 2; i < 8; i++)

{

}

tas_cfg.

cycle_time = LAYER3_SWITCH_EXAMPLE_CYCLE_TIME;

p_gptp_instance->

p_api->

timerCfg(p_gptp_instance->

p_ctrl, LAYER3_SWITCH_EXAMPLE_GPTP_TIMER, &timer_cfg);

p_gptp_instance->

p_api->

start(p_gptp_instance->

p_ctrl, LAYER3_SWITCH_EXAMPLE_GPTP_TIMER);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

for (uint8_t i = 0; i < 2; i++)

{

assert(FSP_SUCCESS == err);

}

while (1)

{

}

}

PSFP Example

MSDU Filter

The below is an example of PSFP MSDU filter.

#define LAYER3_SWITCH_EXAMPLE_PSFP_MSDU_FILTER_ID (0)

#define LAYER3_SWITCH_EXAMPLE_PSFP_MSDU_FILTER_FRAME_MAX_SIZE (60)

#define LAYER3_SWITCH_EXAMPLE_PSFP_MSDU_FILTER_CLEAR_BITMASK (0xFFFF)

void layer3_switch_psfp_msdu_filter_example (void)

{

uint8_t source_port = 0;

uint8_t destination_port = 1;

uint32_t queue_index = 0;

{

.p_descriptor_array = gp_descriptor_pool,

.p_ts_descriptor_array = NULL,

.array_length = LAYER3_SWITCH_EXAMPLE_DESCRIPTOR_POOL_SIZE,

};

memcpy(gpp_ether_buffers[0], gp_send_data, LAYER3_SWITCH_EXAMPLE_TRANSMIT_ETHERNET_FRAME_SIZE);

transmission_descriptor.basic.ds_l = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_LOWER;

transmission_descriptor.basic.ds_h = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_UPPER;

transmission_descriptor.basic.die = 1;

transmission_descriptor.basic.ptr_l = (uintptr_t) gpp_ether_buffers;

transmission_descriptor.info1_tx.fmt = 1;

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

psfp_msdu_filter_cfg.

msdu_filter_id = LAYER3_SWITCH_EXAMPLE_PSFP_MSDU_FILTER_ID;

psfp_msdu_filter_cfg.

maximum_frame_size = LAYER3_SWITCH_EXAMPLE_PSFP_MSDU_FILTER_FRAME_MAX_SIZE;

mac_table_entry.

entry_cfg.p_psfp_msdu_filter_cfg = &psfp_msdu_filter_cfg;

for (uint8_t i = 0; i < 2; i++)

{

assert(FSP_SUCCESS == err);

}

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

}

Meter Filter

The below is an example of PSFP Meter filter.

#define LAYER3_SWITCH_EXAMPLE_PSFP_METER_FILTER_ID (0)

#define LAYER3_SWITCH_EXAMPLE_PSFP_METER_CBS (1000)

#define LAYER3_SWITCH_EXAMPLE_PSFP_METER_CIR (10)

#define LAYER3_SWITCH_EXAMPLE_PSFP_METER_EBS (1000)

#define LAYER3_SWITCH_EXAMPLE_PSFP_METER_EIR (10)

#define LAYER3_SWITCH_EXAMPLE_PSFP_METER_SYSTEM_CLOCK (250)

#define LAYER3_SWITCH_EXAMPLE_PSFP_INFORMATION_RATE_DIVIDE_VALUE (8)

#define LAYER3_SWITCH_EXAMPLE_PSFP_INFORMATION_RATE_1M (1000000)

#define LAYER3_SWITCH_EXAMPLE_PSFP_INFORMATION_RATE_MULTIPLY_VALUE (65536)

#define LAYER3_SWITCH_EXAMPLE_PSFP_METER_FILTER_CLEAR_BITMASK (0xFFFFFFFF)

void layer3_switch_psfp_meter_filter_example (void)

{

uint8_t source_port = 0;

uint8_t destination_port = 1;

uint32_t queue_index = 0;

{

.p_descriptor_array = gp_descriptor_pool,

.p_ts_descriptor_array = NULL,

.array_length = LAYER3_SWITCH_EXAMPLE_DESCRIPTOR_POOL_SIZE,

};

memcpy(gpp_ether_buffers[0], gp_send_data, LAYER3_SWITCH_EXAMPLE_TRANSMIT_ETHERNET_FRAME_SIZE);

transmission_descriptor.basic.ds_l = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_LOWER;

transmission_descriptor.basic.ds_h = LAYER3_SWITCH_EXAMPLE_MAXIMUM_FRAME_SIZE_UPPER;

transmission_descriptor.basic.die = 1;

transmission_descriptor.basic.ptr_l = (uintptr_t) gpp_ether_buffers;

transmission_descriptor.info1_tx.fmt = 1;

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

psfp_meter_filter_cfg.

meter_filter_id = LAYER3_SWITCH_EXAMPLE_PSFP_METER_FILTER_ID;

psfp_meter_filter_cfg.

cbs = LAYER3_SWITCH_EXAMPLE_PSFP_METER_CBS;

psfp_meter_filter_cfg.

cir = layer3_switch_psfp_information_rate_example(

LAYER3_SWITCH_EXAMPLE_PSFP_METER_CIR,

LAYER3_SWITCH_EXAMPLE_PSFP_METER_SYSTEM_CLOCK);

psfp_meter_filter_cfg.

ebs = LAYER3_SWITCH_EXAMPLE_PSFP_METER_EBS;

psfp_meter_filter_cfg.

eir = layer3_switch_psfp_information_rate_example(

LAYER3_SWITCH_EXAMPLE_PSFP_METER_EIR,

LAYER3_SWITCH_EXAMPLE_PSFP_METER_SYSTEM_CLOCK);

for (uint8_t i = 0; i < 2; i++)

{

assert(FSP_SUCCESS == err);

}

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

assert(FSP_SUCCESS == err);

}

◆ layer3_switch_basic_descriptor_t

| struct layer3_switch_basic_descriptor_t |

◆ layer3_switch_descriptor_t

| struct layer3_switch_descriptor_t |

GWCA extended descriptor.

◆ layer3_switch_ts_reception_process_descriptor_t

| struct layer3_switch_ts_reception_process_descriptor_t |

GWCA TS reception process descriptor.

◆ layer3_switch_psfp_msdu_filter_cfg_t

| struct layer3_switch_psfp_msdu_filter_cfg_t |

Configuration of PSFP MSDU filter.

| Data Fields |

|---|

|

uint32_t |

msdu_filter_id |

PSFP MSDU filter ID. |

|

uint32_t |

maximum_frame_size |

Maximum frame size is rejected by PSFP MSDU filter. |

|

layer3_switch_msdu_filter_mode_t |

mode |

PSFP MSDU filter mode. |

◆ layer3_switch_psfp_msdu_filter_info_t

| struct layer3_switch_psfp_msdu_filter_info_t |

Information of PSFP MSDU filter.

◆ layer3_switch_psfp_meter_filter_cfg_t

| struct layer3_switch_psfp_meter_filter_cfg_t |

Configuration of PSFP Meter filter for user.

◆ layer3_switch_psfp_meter_filter_info_t

| struct layer3_switch_psfp_meter_filter_info_t |

Information of PSFP Meter filter.

◆ layer3_switch_psfp_error_status_bitmask_t

| struct layer3_switch_psfp_error_status_bitmask_t |

Bitmasks for clearing error status of throttle mode.

| Data Fields |

|---|

|

uint32_t |

msdu_filter_bitmask |

Bitmask for clearing error status bit of PSFP MSDU filter. |

|

uint32_t |

meter_filter_bitmask |

Bitmask for clearing error status bit of PSFP Meter filter. |

◆ layer3_switch_frer_cfg_t

| struct layer3_switch_frer_cfg_t |

Configuration of FRER feature.

| Data Fields |

|---|

|

uint32_t |

sys_clock |

Timeout check time. |

|

uint32_t |

timeout_enable |

Timeout check valid. |

|

uint32_t |

check_period |

Microsecond prescaler used to creates an internal clock for aging at 1 MHz to derive the timeout 1 kHz clock. |

◆ layer3_switch_frer_entry_t

| struct layer3_switch_frer_entry_t |

| Data Fields |

|---|

|

uint32_t |

take_no_sequence |

Reject frames without R-TAG. |

|

uint32_t |

sequence_history_len |

Sequence history length. |

|

uint32_t |

set_recovery_remaining_tick |

Time in tick before timeout. |

◆ layer3_switch_frer_entry_cfg_t

| struct layer3_switch_frer_entry_cfg_t |

Configuration of FRER entry (individual and sequence recovery).

| Data Fields |

|---|

|

layer3_switch_frer_entry_t |

individual_recovery |

FRER table entry for individual recovery. |

|

layer3_switch_frer_entry_t * |

p_sequence_recovery |

Pointer to FRER entry(sequence recovery) information referenced by FRERN in this FRER entry(individual recovery). |

|

uint32_t |

sequence_recovery_id |

|

◆ layer3_switch_frer_sequence_recovery_status_t

| struct layer3_switch_frer_sequence_recovery_status_t |

Status of FRER sequence recovery table.

| Data Fields |

|---|

|

bool |

learned |

Flags whether the FRER entry(sequence recovery) related to this entry has been learned. |

|

uint32_t |

frer_entry_index |

Real FRER table index of the FRER entry(sequence recovery) related to this entry. |

◆ layer3_switch_descriptor_queue_cfg_t

| struct layer3_switch_descriptor_queue_cfg_t |

Configuration of a descriptor queue.

◆ layer3_switch_cbs_cfg_t

| struct layer3_switch_cbs_cfg_t |

Configuration of Credit Based Shaper.

| Data Fields |

|---|

|

uint8_t |

band_width_list[8] |

CBS band width [%] of each queue. |

|

uint8_t |

max_burst_num_list[8] |

Maximum burst frame number of each queue. |

◆ layer3_switch_port_cfg_t

| struct layer3_switch_port_cfg_t |

Configuration of each Ethernet port.

◆ layer3_switch_descriptor_queue_status_t

| struct layer3_switch_descriptor_queue_status_t |

Status of a descriptor queue.

| Data Fields |

|---|

|

uint32_t |

head |

Index at the head of the queue. This used for GetDescriptor API. |

|

uint32_t |

tail |

Index at the tail of the queue. This used for SetDescriptor API. |

|

bool |

created |

This queue is already created. |

layer3_switch_descriptor_queue_cfg_t

const * |

p_queue_cfg |

Configuration of this queue. |

|

bool |

rx_available |

Indicates whether the queue is available for reception. |

◆ layer3_switch_ipv6_filter_address_offset_t

| struct layer3_switch_ipv6_filter_address_offset_t |

IP address offset for creating IPv6 filter of Layer3 forwarding.

◆ layer3_switch_l3_stream_filter_cfg_t

| struct layer3_switch_l3_stream_filter_cfg_t |

Configuration of stream filter in Layer3 forwarding.

◆ layer3_switch_frame_vlan_tag_t

| struct layer3_switch_frame_vlan_tag_t |

| Data Fields |

|---|

|

uint16_t |

pcp: 3 |

Priority Code Point (3 bit). |

|

uint16_t |

dei: 1 |

Drop Eligible Indicator (1 bit). |

|

uint16_t |

id: 12 |

VLAN ID (12 bit). |

◆ layer3_switch_frame_filter_t

| struct layer3_switch_frame_filter_t |

Frame filter of a MAC/VLAN/Layer3 forwarding entry. Set values for members required for filtering.

| Data Fields |

|---|

|

layer3_switch_table_entry_type_t |

entry_type |

Type of this entry. Select MAC, VLAN or Layer3. |

|

uint8_t * |

p_destination_mac_address |

Destination MAC address. |

|

uint8_t * |

p_source_mac_address |

Source MAC address. |

|

layer3_switch_frame_vlan_tag_t |

vlan_c_tag |

VLAN C-TAG. |

|

layer3_switch_frame_vlan_tag_t |

vlan_s_tag |

VLAN S-TAG. |

|

layer3_switch_ip_version_t |

ip_version |

IP version. Select IPv4, IPv6, or not IP packet. |

|

uint8_t |

protocol |

IP protocol. |

|

uint8_t * |

p_source_ip_address |

Source IP address. |

|

uint8_t * |

p_destination_ip_address |

Destination IP address. |

|

uint16_t |

layer4_source_port |

TCP/UDP source port. |

|

uint16_t |

layer4_destination_port |

TCP/UDP destination port. |

◆ layer3_switch_l3_filter_t

| struct layer3_switch_l3_filter_t |

Store filter information of Layer3 forwarding entry.

◆ layer3_switch_l3_update_config_t

| struct layer3_switch_l3_update_config_t |

Configuration of a L2/L3 update feature for output frames.

◆ layer3_switch_table_entry_cfg_t

| struct layer3_switch_table_entry_cfg_t |

Table entry configuration of MAC/VLAN/Layer3 forwarding.

| Data Fields |

|---|

|

bool |

entry_enable |

Enable or disable entry. If this field is false, entry will be removed. |

|

bool |

security_enable |

Entry is secure or not. |

|

layer3_switch_psfp_msdu_filter_cfg_t * |

p_psfp_msdu_filter_cfg |

|

|

layer3_switch_psfp_meter_filter_cfg_t * |

p_psfp_meter_filter_cfg |

Pointer to configuration of PSFP MDSU filter. Pointer to configuration of PSFP Meter filter.

|

|

layer3_switch_frer_entry_cfg_t * |

p_frer_entry_cfg |

Configuration of the FRER entry(individual recovery) for this L3 entry (set to NULL : FRER is not valid in this L3 entry). |

|

uint32_t |

destination_ports |

Destination ports of forwarding. |

|

uint32_t |

source_ports |

Source ports that enable forwarding of incoming frame. |

|

uint32_t |

destination_queue_index |

Destination queue. This fields is only used when a destination port is CPU. |

|

uint32_t |

internal_priority_update_enable |

Enable to update internal priority. |

|

uint32_t |

internal_priority_update_value |

Internal priority when updating is enabled. |

|

union layer3_switch_table_entry_cfg_t |

__unnamed__ |

|

◆ layer3_switch_table_entry_t

| struct layer3_switch_table_entry_t |

Table entry of MAC/VLAN/Layer3 forwarding.

◆ layer3_switch_forwarding_port_cfg_t

| struct layer3_switch_forwarding_port_cfg_t |

Configuration of forwarding feature for each port.

| Data Fields |

|---|

|

bool |

mac_table_enable |

Enable MAC table and forwarding feature. |

|

bool |

mac_reject_unknown |

Reject frame with unknown MAC address. |

|

bool |

mac_hardware_learning_enable |

Enable hardware learning and migration. |

|

bool |

vlan_table_enable |

Enable VLAN table and forwarding feature. |

|

bool |

vlan_reject_unknown |

Reject frame with unknown VLAN ID. |

|

layer3_switch_vlan_ingress_mode_t |

vlan_ingress_mode |

Select Tag-based VLAN or Port-based VLAN for incoming frame. |

|

layer3_switch_vlan_egress_mode_t |

vlan_egress_mode |

Tagging/untagging mode for outgoing frame. |

|

layer3_switch_frame_vlan_tag_t |

vlan_s_tag |

S-TAG of this port. When egress mode is hardware SC-TAG, add this to outgoing frame. |

|

layer3_switch_frame_vlan_tag_t |

vlan_c_tag |

C-TAG of this port. When egress mode is hardware C-TAG, add this to outgoing frame. |

|

bool |

layer3_table_enable |

Enable Layer3 table and forwarding feature. |

|

bool |

layer3_reject_unknown |

Reject frame that not found in Layer3 table. |

|

bool |

layer3_ipv4_filter_enable |

Enable IPv4 stream filter. |

|

bool |

layer3_ipv6_filter_enable |

Enable IPv6 stream filter. |

|

bool |

layer3_l2_filter_enable |

Enable L2 stream filter. |

◆ layer3_switch_table_t

| struct layer3_switch_table_t |

Forwarding table containing MAC/VLAN/Layer3 forwarding entries.

◆ layer3_switch_table_cfg_t

| struct layer3_switch_table_cfg_t |

Configuration of the forwarding table.

◆ layer3_switch_extended_cfg_t

| struct layer3_switch_extended_cfg_t |

ESWM extension configures each Ethernet port and forwarding feature.

| Data Fields |

|---|

|

ether_phy_instance_t const * |

p_ether_phy_instances[BSP_FEATURE_ETHER_NUM_CHANNELS] |

List of pointers to ETHER_PHY instance. |

|

gptp_instance_t const * |

p_gptp_instance |

Pointer to a gPTP instance. |

|

uint32_t |

fowarding_target_port_masks[BSP_FEATURE_ETHER_NUM_CHANNELS+1] |

List of ports to which incoming frames are forwarded. |

|

uint8_t * |

p_mac_addresses[BSP_FEATURE_ETHER_NUM_CHANNELS] |

|

|

uint32_t |

ipv_queue_depth_list[BSP_FEATURE_ETHER_NUM_CHANNELS][BSP_FEATURE_ESWM_ETHA_IPV_QUEUE_NUM] |

List of IPV queue depth for each port. |

|

uint32_t |

ipv_queue_preemptable_bitmask[BSP_FEATURE_ETHER_NUM_CHANNELS] |

Bitmask of IPV queues that contain preemptable frames. |

|

layer3_switch_preemptable_frame_fragment_size_t |

frame_preemption_fragment_size[BSP_FEATURE_ETHER_NUM_CHANNELS] |

Minimum fragment size of preemptable frame. |

|

layer3_switch_l3_filter_t * |

l3_filter_list |

Filter list of layer3 routing. |

|

uint32_t |

l3_filter_list_length |

Length of Layer3 filter list. |

|

layer3_switch_port_cfg_t * |

p_port_cfg_list[BSP_FEATURE_ETHER_NUM_CHANNELS] |

Configuration for each port. |

|

IRQn_Type |

etha_error_irq_port_0 |

ETHA error interrupt number for port 0. |

|

IRQn_Type |

etha_error_irq_port_1 |

ETHA error interrupt number for port 1. |

|

uint8_t |

etha_error_ipl_port_0 |

ETHA error interrupt priority for port 0. |

|

uint8_t |

etha_error_ipl_port_1 |

ETHA error interrupt priority for port 1. |

|

uint8_t |

gptp_timer_numbers[BSP_FEATURE_ESWM_GPTP_TIMER_NUM] |

List of timer numbers for transmission/reception timestamp. |

◆ layer3_switch_instance_ctrl_t

| struct layer3_switch_instance_ctrl_t |

◆ layer3_switch_tas_entry_t

| struct layer3_switch_tas_entry_t |

Configuration of the gate operation.

◆ layer3_switch_tas_gate_cfg_t

| struct layer3_switch_tas_gate_cfg_t |

Configuration of the gate.

◆ layer3_switch_tas_cfg_t

| struct layer3_switch_tas_cfg_t |

Configuration of the TAS.

| Data Fields |

|---|

|

uint8_t |

gptp_timer_number |

gPTP timer number. |

|

uint32_t |

cycle_time_start_high |

Upper 32 bits of TAS cycle start time [nsec]. |

|

uint32_t |

cycle_time_start_low |

Lower 32 bits of TAS cycle start time [nsec]. |

|

uint32_t |

cycle_time |

TAS cycle time [nsec]. |

|

layer3_switch_tas_gate_cfg_t |

gate_cfg_list[8] |

List of TAS gate configurations. |

◆ layer3_switch_descriptor_type_t

GWCA descriptor type.

| Enumerator |

|---|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_LINKFIX | Linkfix. Control element pointing to next descriptor in chain.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEMPTY_IS | Frame Empty Incremental Start.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEMPTY_IC | Frame Empty Incremental Continue.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEMPTY_ND | Frame Empty No Data Storage.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEMPTY | Frame Empty.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEMPTY_START | Frame Empty Start.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEMPTY_MID | Frame Empty Mid.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEMPTY_END | Frame Empty End.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FSINGLE | Frame Single.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FSTART | Frame Start.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FMID | Frame Mid.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_FEND | Frame End.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_LEMPTY | Link Empty.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_EEMPTY | EOS Empty.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_LINK | Link.

|

| LAYER3_SWITCH_DESCRIPTOR_TYPE_EOS | End of Set.

|

◆ layer3_switch_port_bitmask_t

Bitmasks for each port.

| Enumerator |

|---|

| LAYER3_SWITCH_PORT_BITMASK_PORT0 | Port 0.

|

| LAYER3_SWITCH_PORT_BITMASK_PORT1 | Port 1.

|

| LAYER3_SWITCH_PORT_BITMASK_PORT2 | Port 2.

|

◆ layer3_switch_queue_type_t

Descriptor queue type.

| Enumerator |

|---|

| LAYER3_SWITCH_QUEUE_TYPE_RX | Reception queue.

|

| LAYER3_SWITCH_QUEUE_TYPE_TX | Transmission queue.

|

◆ layer3_switch_descriptor_format_t

Descriptor format type.

| Enumerator |

|---|

| LAYER3_SWITCH_DISCRIPTOR_FORMTAT_BASIC | Using basic descriptor.

|

| LAYER3_SWITCH_DISCRIPTOR_FORMTAT_EXTENDED | Using extended descriptor with additional fields.

|

| LAYER3_SWITCH_DISCRIPTOR_FORMTAT_TX_TIMESTAMP | Using TX timestamp descriptor.

|

◆ layer3_switch_write_back_mode_t

Write back mode.

| Enumerator |

|---|

| LAYER3_SWITCH_WRITE_BACK_MODE_FULL | All fields are updated by hardware.

|

| LAYER3_SWITCH_WRITE_BACK_MODE_DISABLE | No fields are updated by hardware.

|

| LAYER3_SWITCH_WRITE_BACK_MODE_KEEP_DT | Fields exclude DT are updated by hardware.

|

◆ layer3_switch_ip_version_t

IP version options.

| Enumerator |

|---|

| LAYER3_SWITCH_IP_VERSION_NONE | Not IP packet.

|

| LAYER3_SWITCH_IP_VERSION_IPV4 | IPv4 packet.

|

| LAYER3_SWITCH_IP_VERSION_IPV6 | IPv6 packet.

|

◆ layer3_switch_ip_address_direction_t

Direction of IP address.

| Enumerator |

|---|

| LAYER3_SWITCH_IP_ADDRESS_DIRECTION_SOURCE | Use IP source address in stream ID.

|

| LAYER3_SWITCH_IP_ADDRESS_DIRECTION_DESTINATION | Use IP destination address in stream ID.

|

◆ layer3_switch_magic_packet_detection_t

Magic packet detection options.

| Enumerator |

|---|

| LAYER3_SWITCH_MAGIC_PACKET_DETECTION_ENABLE | Enable magic packet detection.

|

| LAYER3_SWITCH_MAGIC_PACKET_DETECTION_DISABLE | Disable magic packet detection.

|

◆ layer3_switch_vlan_mode_t

VLAN detection mode.

| Enumerator |

|---|

| LAYER3_SWITCH_VLAN_MODE_NO_VLAN | Not use VLAN feature.

|

| LAYER3_SWITCH_VLAN_MODE_C_TAG | Detect and use VLAN C-TAG.

|

| LAYER3_SWITCH_VLAN_MODE_SC_TAG | Detect and use VLAN SC-TAG.

|

◆ layer3_switch_vlan_ingress_mode_t

VLAN ingress mode determines whether the switch operates with tagged VLAN or port-based VLAN.

| Enumerator |

|---|

| LAYER3_SWITCH_VLAN_INGRESS_MODE_TAG_BASED | Use VLAN ID of the incoming frame.

|

| LAYER3_SWITCH_VLAN_INGRESS_MODE_PORT_BASED | Use VLAN ID of the incoming port.

|

◆ layer3_switch_vlan_egress_mode_t

VLAN egress mode determines the VLAN tag that is added to output frames.

| Enumerator |

|---|

| LAYER3_SWITCH_VLAN_EGRESS_MODE_NO_VLAN | Frame always outgoing without VLAN TAG.

|

| LAYER3_SWITCH_VLAN_EGRESS_MODE_C_TAG | Frame outgoing with C-TAG of incoming frame.

|

| LAYER3_SWITCH_VLAN_EGRESS_MODE_HW_C_TAG | Frame always outgoing with C-TAG of output port.

|

| LAYER3_SWITCH_VLAN_EGRESS_MODE_SC_TAG | Frame always outgoing with SC-TAG of incoming frame.

|

| LAYER3_SWITCH_VLAN_EGRESS_MODE_HW_SC_TAG | Frame always outgoing with SC-TAG of output port.

|

◆ layer3_switch_ip_protocol_t

IP protocols type.

| Enumerator |

|---|

| LAYER3_SWITCH_IP_PROTOCOL_TCP | IP protocol is TCP.

|

| LAYER3_SWITCH_IP_PROTOCOL_UDP | IP protocol is UDP.

|

◆ layer3_switch_forwarding_r_tag_t

R-TAG filed update options.

| Enumerator |

|---|

| LAYER3_SWITCH_FORWARDING_R_TAG_UPDATE | Incoming frame with R-TAG will be updated with new R-TAG.

|

| LAYER3_SWITCH_FORWARDING_R_TAG_ALWAYS_ADD | ALl incoming frame will be added new R-TAG.

|

| LAYER3_SWITCH_FORWARDING_R_TAG_ALWAYS_ELIMINATE | ALl incoming frame will be removed R-TAG.

|

◆ layer3_switch_l3_filter_bitmask_t

Frame filters options for layer3 forwarding.

| Enumerator |

|---|

| LAYER3_SWITCH_L3_FILTER_BITMASK_MAC_DESTINATION | Enable MAC destination address.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_MAC_SOURCE | Enable MAC source address.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_STAG_ID | Enable VLAN ID of S-TAG.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_STAG_PCP | Enable PCP of S-TAG.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_STAG_DEI | Enable DEI of S-TAG.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_CTAG_ID | Enable VLAN ID of C-TAG.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_CTAG_PCP | Enable PCP of C-TAG.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_CTAG_DEI | Enable DEI of C-TAG.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_IP_SOURCE_ADDRESS | Enable IP source address.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_IP_DESTINATION_ADDRESS | Enable IP destination address.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_PROTOCOL | Enable IP protocol.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_IP_SOURCE_PORT | Enable layer4 source port.

|

| LAYER3_SWITCH_L3_FILTER_BITMASK_IP_DESTINATION_PORT | Enable layer4 destination port.

|

◆ layer3_switch_l3_update_bitmask_t

Enable L2/L3 update feature.

| Enumerator |

|---|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_TTL | Update TTL.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_MAC_DESTINATION | Update MAC destination address.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_MAC_SOURCE | Update MAC source address.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_CTAG_ID | Update VLAN ID of C-TAG.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_CTAG_PCP | Update PCP of C-TAG.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_CTAG_DEI | Update DEI of C-TAG.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_STAG_ID | Update VLAN ID of C-TAG.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_STAG_PCP | Update PCP of C-TAG.

|

| LAYER3_SWITCH_L3_UPDATE_BITMASK_STAG_DEI | Update DEI of C-TAG.

|

◆ layer3_switch_table_entry_type_t

Table entry type for forwarding feature.

| Enumerator |

|---|

| LAYER3_SWITCH_TABLE_ENTRY_TYPE_EMPTY | Entry is not initialized yet.

|

| LAYER3_SWITCH_TABLE_ENTRY_TYPE_MAC | Entry of MAC table.

|

| LAYER3_SWITCH_TABLE_ENTRY_TYPE_VLAN | Entry of VLAN table.

|

| LAYER3_SWITCH_TABLE_ENTRY_TYPE_LAYER3 | Entry of Layer3 table.

|

◆ layer3_switch_table_status_t

Table status for forwarding feature.

| Enumerator |

|---|

| LAYER3_SWITCH_TABLE_STATUS_UNINITIALIZED | Forwarding table is uninitialized.

|

| LAYER3_SWITCH_TABLE_STATUS_INITIALIZED | Forwarding table is initialized.

|

◆ layer3_switch_tas_gate_state_t

TAS gate state.

| Enumerator |

|---|

| LAYER3_SWITCH_TAS_GATE_STATE_CLOSE | Gate is closed.

|

| LAYER3_SWITCH_TAS_GATE_STATE_OPEN | Gate is opened.

|

◆ layer3_switch_rx_timestamp_storage_t

Enable or disable rx timestamp storage.

| Enumerator |

|---|

| LAYER3_SWITCH_RX_TIMESTAMP_STORAGE_DISABLE | Timestamp is not added in the descriptor.

|

| LAYER3_SWITCH_RX_TIMESTAMP_STORAGE_ENABLE | Timestamp is added in the descriptor.

|

◆ layer3_switch_ts_descriptor_queue_status_t

Used or not timestamp descriptor queue.

| Enumerator |

|---|

| LAYER3_SWITCH_TS_DESCRIPTOR_QUEUE_STATUS_UNUSED | TS descriptor queue is unused.

|

| LAYER3_SWITCH_TS_DESCRIPTOR_QUEUE_STATUS_USED | TS descriptor queue is used.

|

◆ layer3_switch_preemptable_frame_fragment_size_t

Fragment size of preemptable frame.

| Enumerator |

|---|

| LAYER3_SWITCH_PREEMPTABLE_FRAME_FRAGMENT_SIZE_64BYTE | Minimum fragment size is 64 byte.

|

| LAYER3_SWITCH_PREEMPTABLE_FRAME_FRAGMENT_SIZE_128BYTE | Minimum fragment size is 64 byte.

|

| LAYER3_SWITCH_PREEMPTABLE_FRAME_FRAGMENT_SIZE_192BYTE | Minimum fragment size is 64 byte.

|

| LAYER3_SWITCH_PREEMPTABLE_FRAME_FRAGMENT_SIZE_256BYTE | Minimum fragment size is 64 byte.

|

◆ layer3_switch_psfp_filter_status_t

Used or not PSFP MSDU filter.

| Enumerator |

|---|

| LAYER3_SWITCH_PSFP_FILTER_STATUS_UNUSED | PSFP filter is unused.

|

| LAYER3_SWITCH_PSFP_FILTER_STATUS_USED | PSFP filter is used.

|

◆ layer3_switch_msdu_filter_mode_t

PSFP MSDU filter mode.

| Enumerator |

|---|

| LAYER3_SWITCH_MSDU_FILTER_NORMAL_MODE | Filtering occurs if LDESCR.TPL[GWCA] is greater than FWPMPCi.MSDUV.

|

| LAYER3_SWITCH_MSDU_FILTER_THROTTLE_MODE | Filtering occurs if LDESCR.TPL[GWCA] is greater than FWPMPCi.MSDUV. Frames with FWEIS2.PMFS[i] set are also filtered.

|

◆ layer3_switch_meter_filter_mode_t

PSFP Meter filter mode.

| Enumerator |

|---|

| LAYER3_SWITCH_METER_FILTER_NORMAL_MODE | Any frame linked to Meter filter i thanks to L3 table received when not enough token is available will be red.

|

| LAYER3_SWITCH_METER_FILTER_THROTTLE_MODE | Any frame linked to Meter filter i thanks to L3 table received when not enough token is available or when FWEIS5.PMRFSi is set will be red.

|

◆ layer3_switch_meter_filter_coupling_status_t

Enable or disable copling flag.

| Enumerator |

|---|

| LAYER3_SWITCH_METER_FILTER_COUPLING_STATUS_DISABLE | When green bucket is full, CIR tokens are lost.

|

| LAYER3_SWITCH_METER_FILTER_COUPLING_STATUS_ENABLE | When green bucket is full, CIR tokens are added to the yellow bucket.

|

◆ layer3_switch_meter_filter_drop_red_frame_t

Drop or not red frames.

| Enumerator |

|---|

| LAYER3_SWITCH_METER_FILTER_NOT_DROP_RED_FRAME | Red frames are not dropped by Meter filter.

|

| LAYER3_SWITCH_METER_FILTER_DROP_RED_FRAME | Red frames are dropped by Meter filter.

|

◆ layer3_switch_meter_filter_dei_handling_policy_t

DEI handling policy for determining a frame color.

| Enumerator |

|---|

| LAYER3_SWITCH_METER_FILTER_DEI_HANDLING_POLICY_IGNORE | Ignore the DEI of the VLAN TAG, and the frame color is determined only by the PCP value.

|

| LAYER3_SWITCH_METER_FILTER_DEI_HANDLING_POLICY_YELLOW | When the DEI of the VLAN TAG is 1, treat it as a yellow frame.

|

◆ layer3_switch_meter_filter_pcp_handling_policy_t

PCP handling policy for determining a frame color.

| Enumerator |

|---|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_GREEN_ALL | Treat all frames as green, regardless of the PCP.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_BELOW_1 | Treat a frame as yellow when the PCP is less than 1.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_BELOW_2 | Treat a frame as yellow when the PCP is less than 2.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_BELOW_3 | Treat a frame as yellow when the PCP is less than 3.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_BELOW_4 | Treat a frame as yellow when the PCP is less than 4.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_BELOW_5 | Treat a frame as yellow when the PCP is less than 5.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_BELOW_6 | Treat a frame as yellow when the PCP is less than 6.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_BELOW_7 | Treat a frame as yellow when the PCP is less than 7.

|

| LAYER3_SWITCH_METER_FILTER_PCP_HANDLING_POLICY_YELLOW_ALL | Treat all frames as yellow, regardless of the PCP.

|

◆ R_LAYER3_SWITCH_Open()

Initializes the switch module and applies configurations. Implements ether_switch_api_t::open.

- Return values

-

| FSP_SUCCESS | Channel opened successfully. |

| FSP_ERR_ASSERTION | Pointer to control block, config structure or extended config structure is NULL. |

| FSP_ERR_ALREADY_OPEN | Control block has already been opened or channel is being used by another instance. Call close() then open() to reconfigure. |

| FSP_ERR_ETHER_ERROR_PHY_COMMUNICATION | Initialization of PHY-LSI failed. |

| FSP_ERR_INVALID_ARGUMENT | Invalid configuration value. |

◆ R_LAYER3_SWITCH_Close()

Disables interrupts and stop module. Implements ether_switch_api_t::close.

- Return values

-

| FSP_SUCCESS | Channel successfully closed. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | Control block is not open. |

◆ R_LAYER3_SWITCH_CreateDescriptorQueue()

Create a new descriptor queue and set it to LINKFIX table. This function must be called before calling R_LAYER3_SWITCH_SetDescriptor and R_LAYER3_SWITCH_GetDescriptor.

- Return values

-

| FSP_SUCCESS | Descriptor created successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | Control block is not open. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_OUT_OF_MEMORY | Descriptor queue list is depleted. |

| FSP_ERR_OVERFLOW | TS descriptor queue is used. |

◆ R_LAYER3_SWITCH_SetDescriptor()

Set descriptor data to a target descriptor.

- Return values

-

| FSP_SUCCESS | Descriptor set successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | Control block is not open. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_INVALID_ARGUMENT | Queue index is invalid. |

| FSP_ERR_NOT_INITIALIZED | This descriptor queue is not created. |

| FSP_ERR_IN_USE | Target descriptor is now running. |

| FSP_ERR_OVERFLOW | Descriptor queue is full. |

◆ R_LAYER3_SWITCH_GetDescriptor()

Get descriptor data from a target descriptor.

- Return values

-

| FSP_SUCCESS | Descriptor got successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | Control block is not open. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_INVALID_ARGUMENT | Queue index is invalid. |

| FSP_ERR_NOT_INITIALIZED | This descriptor queue is not created or target descriptor is not set. |

| FSP_ERR_IN_USE | Target descriptor is now running. |

◆ R_LAYER3_SWITCH_StartDescriptorQueue()

Reload and enable a descriptor queue. In a TX descriptor queue, the queue start transmission. In a RX descriptor queue, the queue start reception.

- Return values

-

| FSP_SUCCESS | Descriptor queue started successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | Control block is not open. |

| FSP_ERR_INVALID_ARGUMENT | Queue index is invalid. |

| FSP_ERR_NOT_INITIALIZED | Target descriptor queue is not created. |

| FSP_ERR_IN_USE | Target descriptor queue is already running. |

| FSP_ERR_INVALID_DATA | Target TX queue have no data. |

◆ R_LAYER3_SWITCH_CallbackSet()

Updates the user callback with the option to provide memory for the callback argument structure.

- Return values

-

| FSP_SUCCESS | Callback updated successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_NO_CALLBACK_MEMORY | p_callback is non-secure and p_callback_memory is either secure or NULL. |

◆ R_LAYER3_SWITCH_ConfigurePort()

Configure Ethernet port features, including callback function for each port.

- Return values

-

| FSP_SUCCESS | Port configured successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_INVALID_ARGUMENT | Port number is invalid. |

◆ R_LAYER3_SWITCH_AddTableEntry()

Add or update an entry of the forwarding table.

- Return values

-

| FSP_SUCCESS | Successfully add/updated an entry into the table. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_OVERFLOW | The number of unsecure entries exceeded the configured value. |

| FSP_ERR_WRITE_FAILED | A hardware error occurred while learning the entry. |

| FSP_ERR_INVALID_ARGUMENT | Target frame or entry type is invalid. |

| FSP_ERR_INVALID_MODE | VLAN feature is disabled and a VLAN entry is passed. |

| FSP_ERR_BUFFER_EMPTY | PSFP MSDU or Meter filter ID is invalid. |

◆ R_LAYER3_SWITCH_SearchTableEntry()

Search an entry from the forwarding table.

- Return values

-

| FSP_SUCCESS | The entry is found successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_NOT_FOUND | The entry is not found in the table. |

| FSP_ERR_INVALID_ARGUMENT | Target frame or entry type is invalid. |

| FSP_ERR_INVALID_MODE | VLAN feature is disabled and a VLAN entry is passed. |

◆ R_LAYER3_SWITCH_ConfigureTable()

Configure and initialize an forwarding table.

- Return values

-

| FSP_SUCCESS | Table configured successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_WRITE_FAILED | Failed to add entries. |

◆ R_LAYER3_SWITCH_GetTable()

Get a pointer to the forwarding table.

- Return values

-

| FSP_SUCCESS | Table got successfully. |

| FSP_ERR_ASSERTION | Pointer to control block is NULL. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_INVALID_MODE | VLAN feature is disabled and a VLAN entry list is passed. |

◆ R_LAYER3_SWITCH_ConfigureTAS()

Configure Time Aware Shaper feature.

- Return values

-

| FSP_SUCCESS | TAS configure successfully. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_INVALID_POINTER | Pointer to a argument is NULL. |

| FSP_ERR_INVALID_ARGUMENT | Port number is invalid. |

| FSP_ERR_UNSUPPORTED | TAS feature is not enabled in the configuration. |

◆ R_LAYER3_SWITCH_EnableTAS()

Enable Time Aware Shaper feature.

- Return values

-

| FSP_SUCCESS | TAS enabled successfully. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |

| FSP_ERR_INVALID_ARGUMENT | Port number is invalid. |

| FSP_ERR_UNSUPPORTED | TAS feature is not enabled in the configuration. |

◆ R_LAYER3_SWITCH_PsfpClearErrorStatus()

Clear error status bit of throttle mode.

- Return values

-

| FSP_SUCCESS | Status bit cleared successfully. |

| FSP_ERR_ASSERTION | A required pointer is NULL. |

| FSP_ERR_NOT_OPEN | The control block has not been opened. |